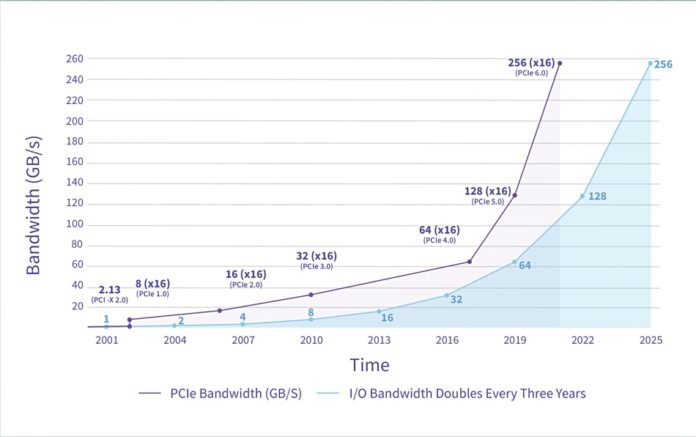

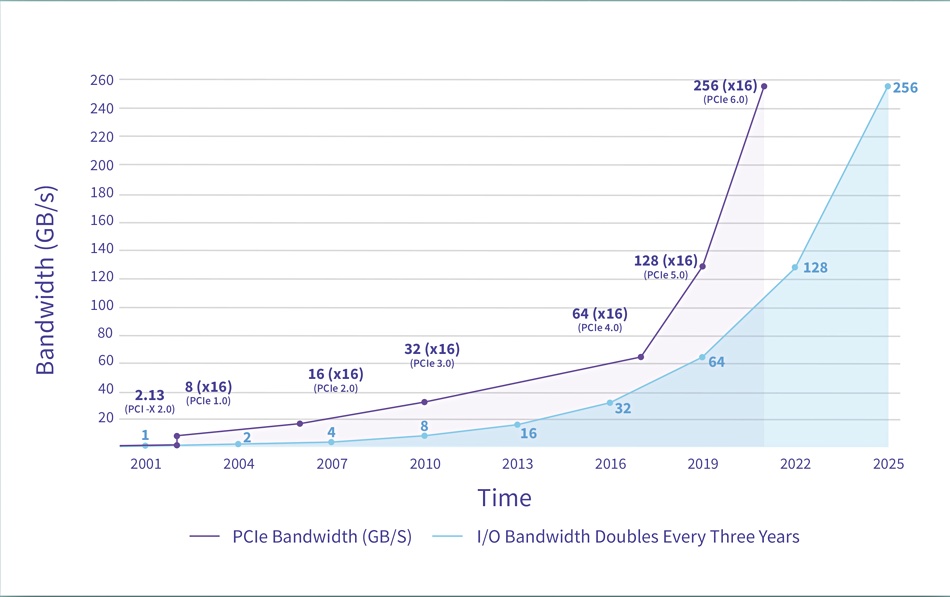

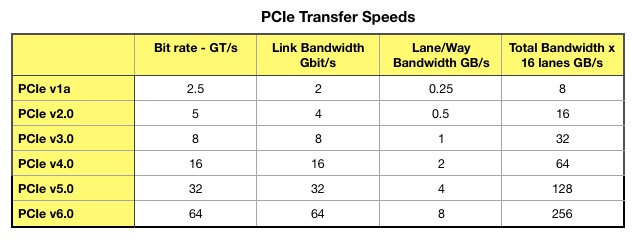

The PCIe SIG has released the official PCIe gen 6 specification, which doubles PCIe 5 speed to 256GB/sec across 16 lanes.

PCIe system designers can use this to double existing bandwidth across PCIe lanes, or halve the number of lanes for the same bandwidth — thus freeing up PCIe lane slots.

Al Yanes, PCI-SIG chairperson and president, issued a quote: “PCI-SIG is pleased to announce the release of the PCIe 6.0 specification less than three years after the PCIe 5.0 specification. PCIe 6.0 technology is the cost-effective and scalable interconnect solution that will continue to impact data-intensive markets like datacenter, artificial intelligence/machine learning, HPC, automotive, IoT, and military/aerospace, while also protecting industry investments by maintaining backwards compatibility with all previous generations of PCIe technology.”

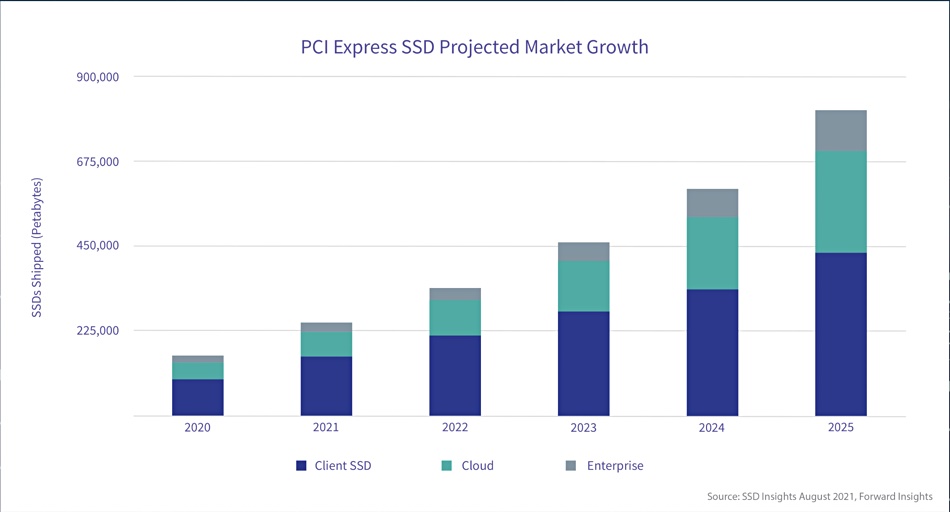

Greg Wong, founder and principal analyst at Forward Insights, said: “The PCI Express SSD market [is] forecasted to grow at a CAGR of 40 per cent to over 800 exabytes by 2025. With the storage industry transitioning to PCIe 4.0 technology and on the cusp of introducing PCIe 5.0 technology, companies will begin adopting PCIe 6.0 technology in their roadmaps to future-proof their products and take advantage of the high bandwidth and low latency that PCI Express technology offers.”

NVMe data access across a PCIe 6 bus should be faster, which will increase application execution speed. With the CXL (Compute eXpress Link) bus being developed on a PCIe 5 base, and capable of providing dispersed memory configurations, a future version based on PCIe 6 should reduce the latency of memory accesses across the link.

We expect the first SSDs supporting PCIe 6 to appear in the 2023–2024 timeframe, with gaming system designers leading the way.