Panmnesia is developing technology enabling the connection of hundreds of memory devices across multiple servers.

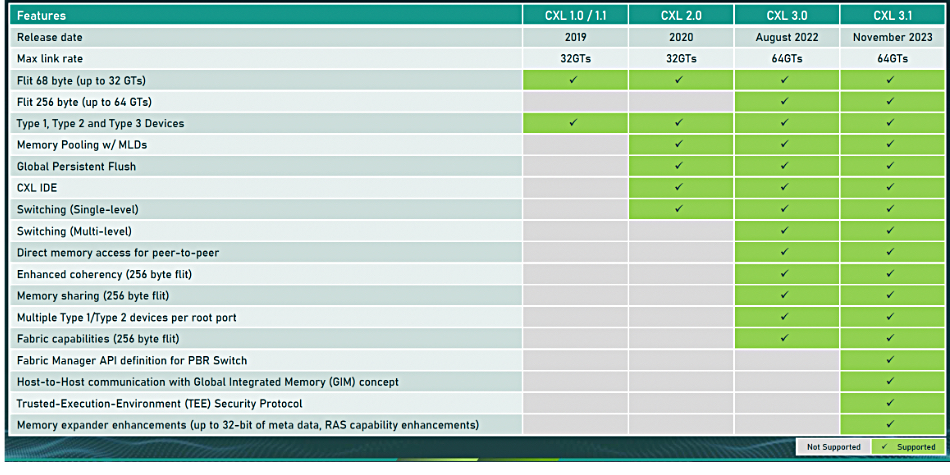

The Korean startup supports v3.1 of Computer Express Link (CXL). This addresses remote memory pooling and PCIe 6.0 interconnects to enable servers, both CPU and GPU-based, to share external memory, combining it with their own direct-attached DRAM to increase memory capacity and their ability to run memory-bound AI workloads, Panmnesia says.

Panmnesia CEO Myoungsoo Jung said in a presentation: “Our CXL 3.1 switch will not only reduce server operating costs but also enable practical memory expansion in terms of performance, thanks to our high performance CXL IP.”

CXL 3.0 enables a pool of CXL switch-accessed external memory to be shared between host computers with coherent caches in the hosts and the CXL memory endpoints or expanders. CXL 3.1 added several incremental features to this base:

- CXL fabric improvements and extensions with, for example, scaleout CXL fabrics using Port-Based Routing (PBR)

- Trusted-Execution-Environment Security Protocol (TSP) allowing virtualization-based Trusted Execution Environments (TEEs) to host confidential computing workloads

- Memory expander improvements with up to 32-bit of metadata and RAS capability enhancements

Earlier this year, Panmnesia introduced a CXL-enabled AI accelerator. It is developing a v3.1 CXL switch chip, codenamed Shattuck, and System on Chip, and claims its CXL 3.1 IP has latency below 100 nanoseconds, which would be a world first.

The switch chip connects various system components such as CPUs, GPUs, memory, and accelerators, managing end-to-end communication between them. With a cascading, multi-level concept, it will allow multiple switches to be connected in numerous levels or configured in a fabric-like structure, enabling the connection of hundreds of devices across multiple servers. And it will support previous CXL standards, type 1, 2, and 3 devices, and all subprotocols of CXL – CXL.mem, CXL.cache, and CXL.io.

Get more details of Panmnesia’s CXL 3.1 technology here (registration required).

Panmnesia plans to provide its CXL 3.1 switch chip to customers by the second half of 2025.