The seventh generation PCIe specification draft has been released, with the full spec scheduled for publication sometime in 2025.

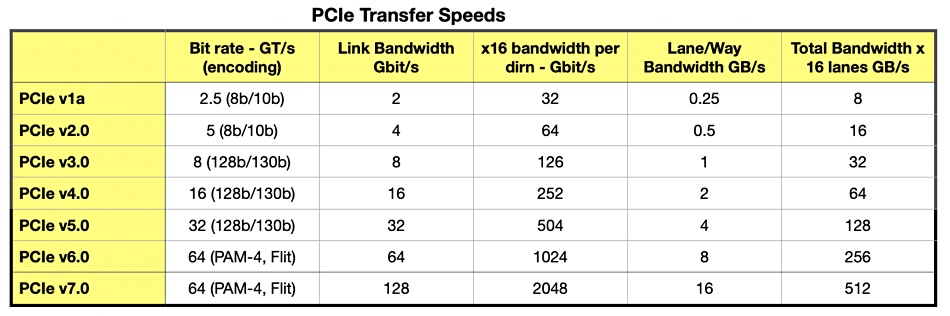

The Peripheral Component Interconnect Express (PCIe) bus is used by PCs and servers to connect CPUs, networking, graphics cards, and storage devices. It is used to transmit data between them. As with preceding PCIe generations, this one doubles the PCIe bus transfer speed, from gen 6’s 64 Gbps link bandwidth to 128 Gbps. That’s 512 GBps bandwidth across 16 lanes.

A blog by PCI-SIG president Al Yanes says: “Progress continues on the PCI Express (PCIe) 7.0 specification, which PCI-SIG announced at US DevCon in June 2022. Thanks to the hard work of our technical work groups, we are pleased to announce that version 0.5 is now available for member review. This is the official first draft of the specification, incorporating all the feedback we received from members after the release of Version 0.3 in June 2023.”

Yanes says gen 7 PCIe is aimed at the high bandwidth needs of 800G Ethernet, artificial intelligence/machine learning, hyperscale datacenters, HPC, quantum computing, and the public cloud. The intended feature list includes:

- Delivering 128 GT/s raw bit rate and up to 512 GB/s bi-directionally via x16 configuration

- Utilizing PAM4 (Pulse Amplitude Modulation with 4 levels) signaling

- Focusing on the channel parameters and reach

- Continuing to deliver low-latency and high-reliability targets

- Improving power efficiency

- Maintaining backwards compatibility with all previous generations of PCIe technology

PCIe gen 6 enables CXL v3.0 memory pooling, sharing, and multi-level switching support. PCIe 7 will increase the bandwidth available for such external memory sharing and pooling. A program to verify compliance with the PCIe 7 standard is expected to be available in 2027 with products released after that.

PCI-SIG members can access the v0.5 PCIe 7.0 spec on the members workspace on Causeway. Non-members can join here.