How does Micron view the world of CXL (Computer eXpress Link)? Blocks & Files had the opportunity to talk about this with Ryan Baxter, a Micron senior director of marketing and the segment lead for the datacenter (cloud and networking) area.

The background here is that Micron exited Optane (3D XPoint) manufacturing in favor of developing CXL-attached memory products in March last year. Seventeen months later, how has its thinking developed? We had a great conversation with Ryan, learning a lot, and have tidied the Otter.ai transcription of our messy questions and his answers.

Blocks & Files: What are your views on Optane and memory expansion?

Ryan Baxter: When you looked at 3D XP, and the ability to use what was an interesting technology, you know, along several interfaces, the problem was that it was proprietary, right? There wasn’t a quote unquote, standard – it was a protocol defined by essentially a single company. And it was kind of stuck in its tracks because of the language standards.

Blocks & Files: How does Micron view CXL possibilities for its memory business?

Ryan Baxter: With CXL I think the the game has completely changed. The entire industry is behind the definition. Certainly when you when you look at media manufacturers, technology integrator groups, developers, software folks, everybody is all in and … singing from the same song sheet when it comes to CXL 2 or 3.0 standards. Everybody has a map this time, and everybody has a key to unlocking innovation. I think that’s really why it’s so different this time around.

It’s also generally a protocol that’s flexible, and extremely non-deterministic. … Customers really want that flexibility … to leverage CXL to expand memory footprint, to extend memory bandwidth to coherently leverage accelerators on the same exact electricals. … The building blocks just became significantly greater in terms of what you can do with with the server.

Fankly, servers needed something like this. Whether it was the CXL or something else that needed to come along, there’s very real near-term existential issues coming up right around the corner, from a server platform perspective. Core count growth [is] 20, 25 percent year on year … and from a memory innovation perspective, whether that be scaling in terms of capacity or scaling in terms of bandwidth, it’s nowhere near catching up or keeping up. Those cores need capacity, they need bandwidth. And the memory channels … aren’t able to keep up by themselves, and you need something like a CXL interface to help them out.

Blocks & Files: What about 512GB capacity DDR5 memory to increase memory capacity?

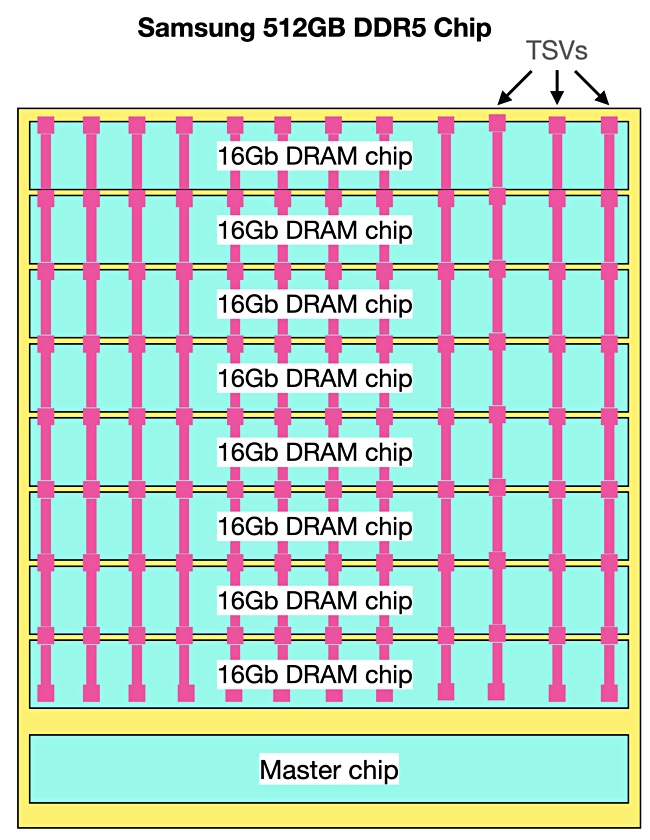

Ryan Baxter: A 512GB capacity is possible in DDR5, it certainly is. But what that leverages is stacked DRAM and in the DDR5 realm, because that DRAM has to signal at least 40 to 100 Mega transfers per second – that gets you out of the ability [to use] a traditional wire bond. Now wire bond is fairly cost-effective when it comes to industry feasibility. Once you have to go to a TSV-based stack because of the signal integrity, TSV, meaning through Through Silicon Vias, it’s both a front-end process as well as a back-end process and a number of steps required to get that stack just right. And that’s before you include yield loss associated with it. And so those 512GB modules, although possible, are extremely expensive.

Whenever you stack the RAM, and in a TSV-based fashion, your cost per bit goes nonlinear extremely quickly. You know, customers that are there, you know, kind of concerned about paying 35, 40, 45 percent of their entire system BOM cost. When you get into the mode of TSV-based items, that number becomes 60, 70 percent. And I don’t think anybody’s happy about that.

That’s why we embrace CXL. It really allows you to create a pressure release valve in the server. [It] really is required for customers to number one, meet their TCO goals and number two, for the industry to do full time innovation. It really is a standard for everyone and and it enables companies like Micron to really bring to the table innovative technologies for its customers that we never were able to do before because there simply wasn’t an interface available before.

Blocks & Files: You mentioned innovative technologies. Micron has standard DRAM and you have high-bandwidth memory. Are there going to be others?

Ryan Baxter: As a memory developer and manufacturer and supplier we are always looking at at new candidates outside of the standard DDR4 DRAM or 5 and HBM. We’re looking at all sorts of candidates. The hopper for our R&D is filled with really interesting technologies. … What’s interesting about CXL is it allows allows you to dial in the kind of interesting aspects of the technology you want to use and and not be shackled. … All of your media control is done on the backside and it’s obfuscated from whatever the user will have to do. Certainly we’re taking a hard look at potential candidates with nothing announced as of now, but the potential is there to to leverage more than just potentially DRAM or HBM or CX.

Blocks & Files: Can I ask you about two particular types of possible innovative memory? One is 3D DRAM – is that something Micron is looking at, and the other is storage-class memory.

Ryan Baxter: We’ve made it public that at some point we’ll need to go to some some form of 3D DRAM just to maintain our our scaling capability in the standard DRAM roadmap. … Most certainly you’ll see 3D DRAM operate behind a CXL interface.

When it comes to storage-class memory again, we haven’t made any formal announcements … but certainly the capability is there, the potential is there. … Again, it’s a prime candidate for a media that can then bolt on CXL. Nothing formally announced but nothing that precludes us from being able to take a look.

Blocks & Files: Kioxia has announced a second generation of its XL_FLASH which is slightly faster than normal flash. The new generation has a great slug of MLC flash behind the SLC front end. That seems like a tiered SSD. I think Samsung’s has a drive with DRAM at the front and then NAND behind that. Both companies are using traditional technologies, standard DRAM, standard, NAND, without going to anything exotic like phase change memory or M-RAM or anything like that. Would that be Micron’s direction, rather than to go after exotic technologies?

Ryan Baxter: Nothing announced, as of now, but memory tiering or storage tiering is not a new idea. It’s been around for a number of years, perhaps decades. The reason is people want to take the best of one technology and combine it with the best aspects of another technology. In the case of tiered DRAM and NAND – you’re taking the the performance aspects of DRAM, and the cost and scalability aspects of NAND and pushing them together. Of course, in this world, nothing comes for free. You have to think about the implications on the entire stack for doing that meaning, how is your OS, your middleware, your applications? How are they going to have to adapt to be able to take advantage of it?

What about an exotic technology? It might be that that you want the persistence of a media that doesn’t forget, but you want it very fast, like DRAM. Maybe those two are the qualities you want to combine in this emerging media. There are gaps when you when you look at DRAM when combined with with NAND, when you look at other standard technologies combined with other standard technologies. … And that’s where emerging media comes into play – where we feel that there are a number of gaps. … That still lies sort of unaddressed, if you will, and … that’s why you would choose a non-traditional media to fill those gaps.

Comment

Ryan couldn’t comment on the Memory Coalition of Excellence idea being promoted by Micron and Western Digital – the news had broken to recently for that. MIcron today announced, in connection with US CHIPS and Science act, it was going to invest $40 billion in building semiconductor fabs in the USA between now and 2030.

Our sense of Micron’s storage-class memory thinking is that it is far from announcing any product effort involving exotic new technologies, such as some resistive RAM variant. We think tiered DRAM and tiered NAND drives might be working their way through its R&D labs, and that 3D NAND is present there as well.

TSV-based stacked DRAM was not viewed favorably at all. Our take-away thinking is that Micron is set on developing its 3D NAND and on developing 3D DRAM that can sit on the CXL link. Tiered memory products that are accessed over CXL seem a little less likely.