SK hynix has boosted DDR5 memory speed with a buffer between the CPU and DRAM which can accept parallel reads from 2 banks.

This DDR5 Multiplexer Combined Ranks (MCR) Dual In-line Memory Module (DIMM) was developed with a buffer from Renesas and Intel’s MCR technology. SK Hynix says DDR5 DIMMs can output 4.8Gbps and its MCR DIMM is at least 80 percent faster than that.

Sungsoo Ryu, SK hynix’s head of DRAM Product Planning, claimed: “SK hynix delivered another technological evolution for DDR5 by developing the world’s fastest MCR DIMM.”

A DIMM has several memory chips on its board. DDR5 (Double Data Rate 5) has double the bandwidth and capacity of the previous DDR4 memory standard. SK Hynix shipped its first DDR5 modules in November 2018.

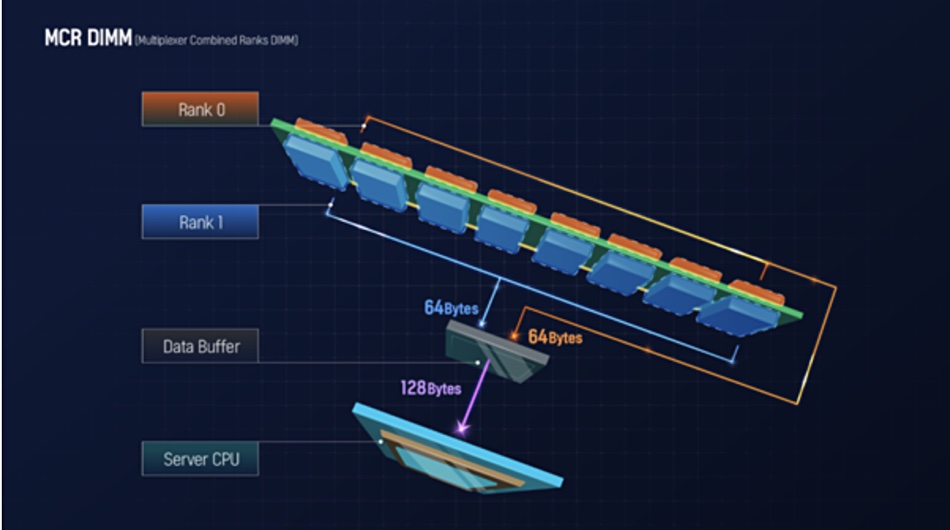

The more DRAM speed and capacity the better, as server and PC CPUs can get through more work with less waiting for memory contents to be read or written. DDR5 memory is organized into ranks, being part of the memory that typically refers to 64 bytes of data to be transferred to the CPU as a bundle. The MCR DIMM is a module product with multiple DRAM chips attached to the board and improved speed as a result of two ranks operating simultaneously.

Through this dual rank operation SK hynix’s MCR DIMM enables the transmission of 128 bytes of data to the CPU in one operation instead of 64. This supports a data transfer rate of 8Gbps, not quite twice the 4.8Gbps rate of unbuffered DDR5 DIMMs.

The development effort by SK hynix, Renesas, and Intel MCR DIMM has been underway since 2019. Sk hynix said a significant market for MCR DIMMs could be high-performance computing. It is planning to bring the product to mass production in the future, but no date was signalled.

Dr Dimitrios Ziakas, VP of Memory and IO Technologies at Intel, said: “We look forward to bringing this technology to future Intel Xeon processors and supporting standardization and multigenerational development efforts across the industry.” There is a hint there, a slight hint, that non-Intel processors could support this in the future.