Details of the “last Optane Persistent Memory” have been shared by Twitter poster HXL who revealed what they claim (and what looks very much like) an Intel slide.

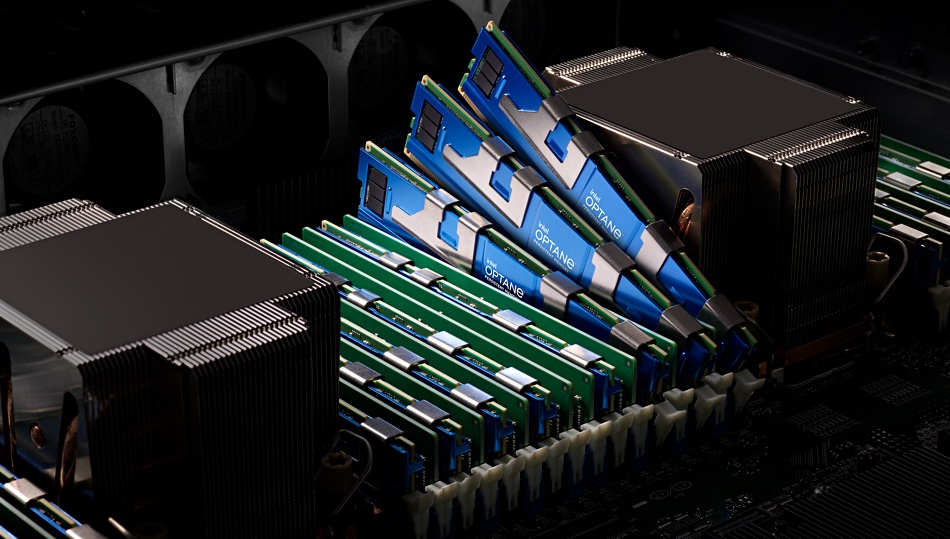

Optane Persistent Memory (PMem) is Intel’s 3D XPoint chips mounted on a DIMM carrier that plugs into a processor’s memory bus via a DIMM socket. Gen 1, the PMem 100 series, code-named Apache Pass, using the original two-deck XPoint chips, was introduced in 2018 with the PMem 200 series, known as Barlow Pass, built from gen 2, four-deck chips, arriving in 2020.

The PMem 300 series, Crow Pass, was supposed to land near the end of 2022, according to Intel VP and GM Kristie Mann. It was slated to use the same gen 2 XPoint chips because manufacturing has ceased and Intel has walked away from further Optane development. It still has gen 2 XPoint chip inventory and this will be used for the PMem 300 series.

PMem 200 DIMMs were optimized for gen 3 Xeon processors – Cooper Lake and Ice Lake – with PMem 300 designed for use with Sapphire Rapids gen 4 Xeons and Emerald Rapids gen 5 Xeon CPUs.

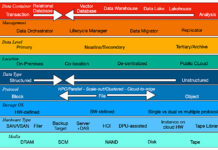

You can see the “leaked slide” here.

It appears to use different performance and interconnect details than we have seen before with Optane DIMMs. The DDR-T2 interface enables 4TB of Optane PMem per socket. We understand that the T value of 1 or 2 refers to the difference between memory cell and memory bus clock cycles. With DDR-T2 the bus is timed (clocked) at double the memory cell speed.

PMem 300 operates at 4,000 to 4,400 MTps, much faster then PMem 200’s up to 3,200 MTps.

Data transfer speed is referenced by random and sequential bandwidth. Up until now we have only seen sequential bandwidth numbers for PMem products. PMem 100 ran at up to 6.8GBps reading and 2.3GBps writing. The PMem 200 products operated at up to up to 8.10GBps for reads and 3.15GBps for writes.

The slide details both 2RW1 random and sequential bandwidth. We understand 2R1W refers to two reads and one write, meaning a multi-port memory supports two read ports and a single write port. The slide has different read and write numbers for the PMem 100 and 200 products than the ones we have used above:

- PMem 100 – 1GBps random and 4GBps sequential bandwidth

- PMem 200 – 1.21GBps random and 4.83GBps sequential bandwidth

- PMem 300 – up to 3GBps random and 6GBps sequential bandwidth

The PMem 300 supports an up to 25 percent opportunistic bandwidth increase per CPS, which could mean calls per second. I’m told that memory bandwidth boost is a feature where the Optane DIMM temporarily exceeds its TDP (Thermal Design Point) to run faster if thermal headroom is available.

Lastly, PMem 300 supports the same operating modes as the original PMem 100 series: App Direct, Memory Mode, and Mixed Mode.

Existing Optane PMem users will be able to consider upgrading to the PMem 300 series when they move to Sapphire Rapids Xeons to get an extra performance boost. They can then use PMem 300 DIMMs with gen 5 Xeons if the chips persist in Intel’s inventory.

Bootnote

Intel and Micron’s 3D XPoint media is an implementation of Phase-Change Memory in which an electrical current is used to change the state of a chalcogenide glass material from crystalline to amorphous and back again. The two states have different resistance levels and these are used to signal binary ones and zeroes. Each state is persistent or non-volatile.

The XPoint media is fabricated in cells which are laid out in a two-layer crosspoint array. Access time is faster than NAND flash but slower than DRAM, with writes taking about three times longer than reads.

Optane can be implemented as a memory bus-connected DIMM (PMem) or as an NVMe-connected SSD. Read more of Optane and 3D XPoint’s history here.