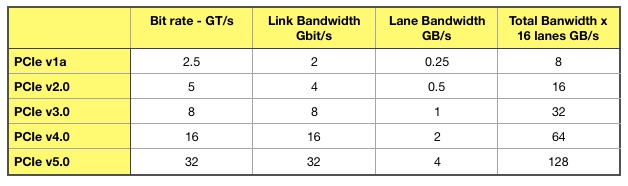

The PCI-SIG has released PCIe 5.0, a specification that quadruples PCIe speed, with 16 lanes running at 128GB/sec.

Servers using the PCIe 5.0 bus should run applications faster as their IO transfers complete in less time.

PCIe speeds are represented as the raw bit rate and also gigatransfers/second (GT/s) as the bits transferred across the bus include overhead bits as well as data bits. The actual data rate can be approximated though, and our table shows this as a per lane rate and aggregated across 16 lanes.

PCIe 4.0 standards were announced some two years ago. The update has taken 18 months to produce and is backwards-compatible, as with previous versions of the specification.

Indeed the PCI-SIG has produced the updates so quickly that hardware system builders may skip PCIe 4.0 entirely to go straight to v5.0.

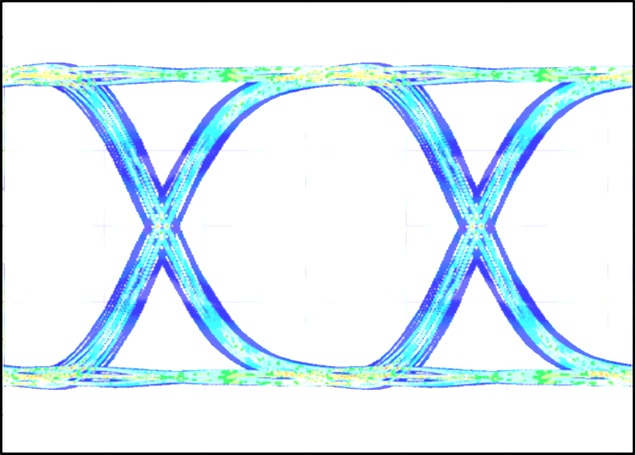

PCI-SIG Astera Labs has announced PCIe v5.0 retimer technology to help hyperscalers to tie processors, GPU accelerators and storage nodes together across PCIe. Retimers are needed to ensure PCIe signal integrity across links.

Applications in the artificial intelligence, machine learning, gaming, visual computing, storage and networking areas are identified by the PCI SIG as potential for v5.0 systems.

PCIe members can get the v5.0 specifications here.