Silicon valley startup and new unicorn Astera Labs has raked in $150 million in funding on top of delivering its Leo CXL Memory pooling and sharing controllers.

CXL, the Compute Express Link, is the feted technology of the day, freeing servers from socket-restricted memory limits and enabling huge and dynamic increases in memory capacity for running machine learning and analytics applications with enormous data sets. Memory will be pooled in CXL-connected memory boxes and dynamically allocated to servers as needed. CXL can also be used to interconnect servers and various accelerators with shared and coherent memory resources. This will help enable fast processor type switching while avoiding time-consuming storage IO to feed memory in an accelerator hardware device when application code needs to execute there.

Astera Labs co-founder and CEO Jitendra Mohan said: “This latest funding round is a testament that we are not only invested in the right growth markets such as Cloud, Artificial Intelligence/Machine Learning, and Hyperscale infrastructure, but that we are also able to consistently execute and deliver breakthrough connectivity products that are critical to our customers and partners.”

The company was founded in Santa Clara in 2017 by Mohan, chief business officer Sanjay Gajendra, and chief product officer Casey Morrison, all ex-Texas Instruments engineers and execs. It raised $35 million in seed and 2018 A-round funding, $50 million in a 2021 C-round, and now $150 million in a D-round to take the total raised to $235 million. Its valuation is now $3.15 billion.

The D-round was led by Fidelity Management with cash also coming from existing investors, including Atreides Management, Intel Capital, and Sutter Hill Ventures. Stefan Dyckerhoff, managing director at Sutter Hill and Astera board member, said: “I’m extremely impressed by the company’s ability to assert itself as the leader in the cloud infrastructure market that increasingly demands purpose-built connectivity solutions to remove performance bottlenecks.”

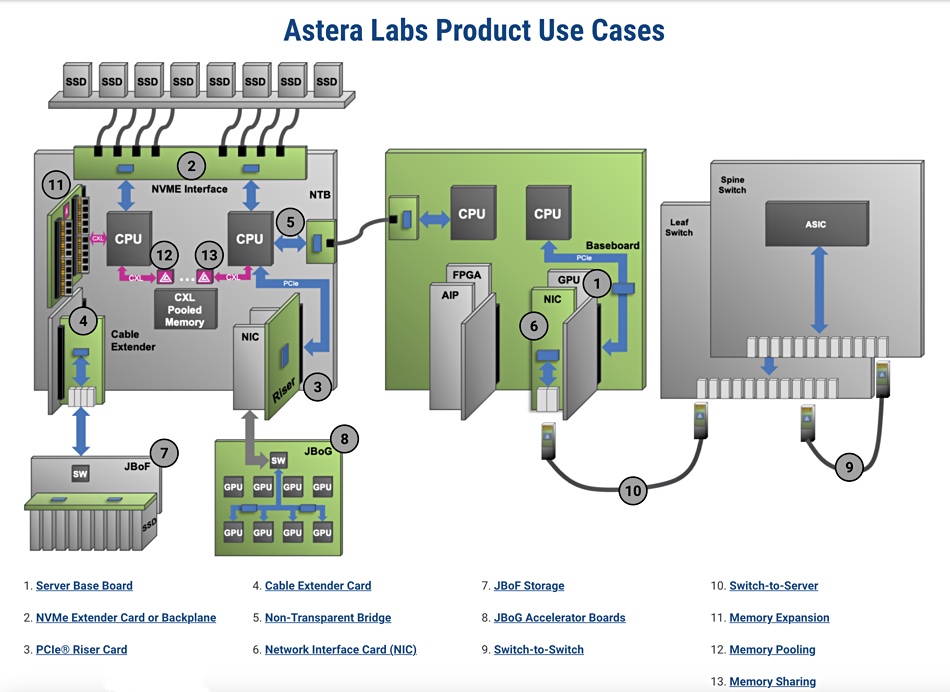

Astera has built three product technologies for its envisioned composable, disaggregated, and scalable datacenter infrastructure: Taurus smart cable modules said to overcome a 400/800Gbps bottleneck in datacenters; Aries PCIe/CXL smart retimers to ensure signal integrity between CXL start and end-points; and the most recent one, the LEO CXL memory controllers, now in a pre-production phase. Astera has done this in co-operation with potential OEM partners such as Broadcom, Nvidia, and Samsung, with much interoperability testing.

It’s also being canny with board membership, having appointed Alexis Black Bjorlin. She leads the Infrastructure Hardware team at Meta and was previously SVP and GM of Broadcom’s optical systems division and corporate VP of the Data Center Group and GM of the Connectivity Group at Intel. Michael Hurlston, Synaptics president and CEO, has also joined Astera’s board. Such senior and deep industry contacts will be highly valued at Astera, helping its product development direction and smoothing the takeoff for potential OEM deals.

Astera has research and development centers in Vancouver and Toronto and is hiring staff there and elsewhere in North America and also Asia as it scales up its business operation.

Get a Leo Smart Memory Controller brief here.