Startup Smart IOPS has burst out from stealth mode with a line of enterprise-class PCIe 3 and 4 SSDs using its own controller chip that it says treats data blocks like packets to achieve vastly increased IOPS and low latency.

The company was started in 2013 by ex-SanDisk engineers to target the high-end enterprise SSD market. It has taken in some $20 million of funding from investors. With that it has devised its own controller chip hardware architecture and firmware, and built and shipped SSDs to customers such as China Telecom and adtech company TheTradeDesk.

Co-founder, president and CEO Ashutosh Das told B&F at an IT Press Tour briefing: “We started [generating] revenue in 2021. We’re selling to large enterprises like NASA and Verizon Media and have tens of customers with a strong pipeline.” SmartIOPS has “already shipped thousands of units” with around 10PB of installed capacity.

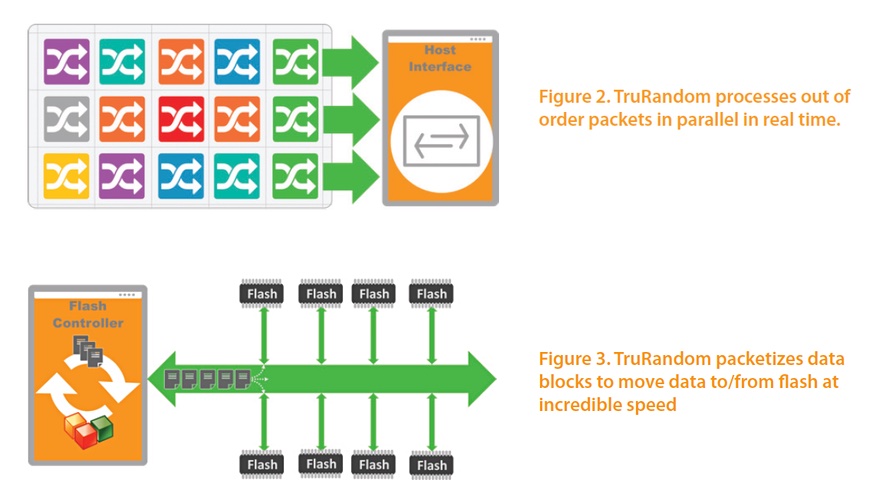

The key Smart IOPS development, we’re told, is its TruRandom controller which has logic enhancing data pattern recognition heuristics for data access to make random and sequential I/O requests become indistinguishable. This is achieved by treating incoming data blocks as out-of-order packets and processing them in parallel.

Working alongside Das – who was previously at Juniper and Sun Microsystems – is chief scientist and co-founder Manuel d’Abreu, who has has a wide-ranging technology background, including spells at AMD and also at Sun.

A Smart IOPS white paper explains: “The performance boost and low latency capabilities of TruRandom are achieved by implementing a fully optimized non-blocking, asynchronous SSD controller architecture.” The controller has a non-blocking, out-of-order fabric connecting its components including the flash dies.

The white paper says: “Storage and networking mediums share one core service component – data shoveling and moving bits from point A to point B. Inspired by the networking best practices, TruRandom hones in on that commonality and aims to perfect it. Its architecture fully leverages the NVMe parallelism (Figure 2) by laying out a fabric inside the controller to move packetized out-of-order data in a non-blocking manner as illustrated in Figure 3 below.”

“All activities internal to the SSD that take a long time, such as Garbage Collection (GC), internal logging and metadata table updates are postponed until all Input/Output (I/O) requests have cleared the queues and the host Operating system (OS) is not waiting for any additional I/O.”

Smart IOPS has 17 patents covering its IP with more filed, and the patent list includes deduplication (US patent 20200218462) on the chip plus error checking and correction.

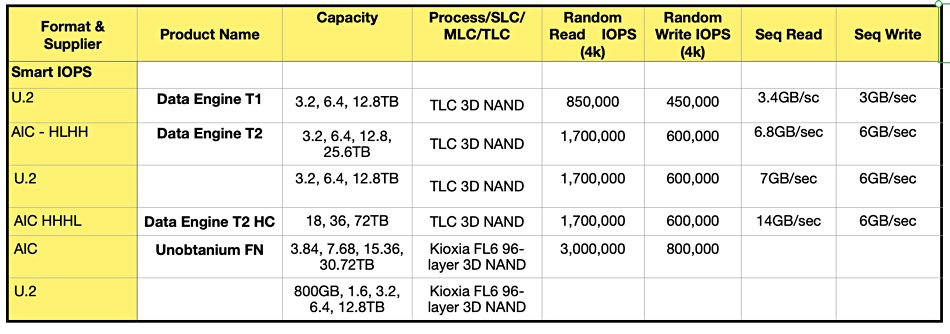

The controller has been used to build four different NVMe SSD products; three branded Data Engine, and one Unobtanium:

The Data Engine T1 HP is a PCIe 3 product whereas the Data Engine T2 HP comes in both gen 3 and 4 PCIe form. The performance doesn’t vary much as the controller is operating the NAND at close-to-wire speed and the speed and capacity of the digital pipe connecting the SSD to the host is not the limiting factor.

These are all high-performance products using either Kioxia or Micron TLC (3bits/cell) 3D NAND chips. QLC (4bits/cell) products are in development. The Data Engine T2 HC is a high-capacity product with a PCIe 3 x 8 lane interface.

The latency numbers are impressively low. The DataEngine T2 HP has 5μs write and 60μs read latency with a queue depth of 1. Bump that up to 128 and the numbers are 11μs write and 200μs read. This performance level is said to be maintained for five years and the products typically have a three drive writes per day (DWPD) rating for that period as well.

The fourth product is a storage-class memory device using Kioxia FL6 NAND and is called Unobtainium, a dig at Intel’s now cancelled Optane 3D NAND technology. Its latency number is 16μs at a queue depth of 1. It pumps out 3 million random read IOPS and supports 15 DWPD for five years.

Functional Storage Drive

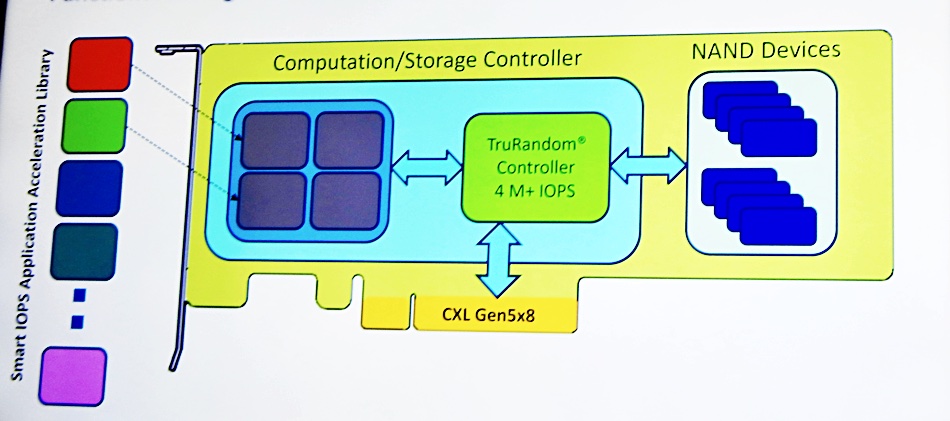

Smart IOPS is developing a Functional Storage Drive (FSD), which is a completely different product. It has FPGAs on the system-on-chip board and the ability to dynamically load and reload new application code into them. Think next-generation computational storage.

A diagram shows four FPGA blocks in a system diagram; there could be more, with code loaded from an application acceleration library. Das said: “The CPU could trigger a load function into the FPGA and so program it with fresh firmware on the fly.”

The FSD will probably have an 8TB capacity and Smart IOPS is working with Intel and AMD (Xylinx) on the FPGA component. This looks to be a 2023 or even 2024 product.

Das said: “The market is moving towards this… Samsung has a device with a Xilinx FPGA inside it,” which represents an initial step towards the concept, with Smart IOPS’s integrated system further along the development path. It’s a firm step onward from computational storage, like that of ScaleFlux, with fixed function hardware.