In the tense game of poker whose stakes are defining the component interconnect post-PCIe, the Gen-Z consortium has folded. It will be absorbed into the Computer Express Link (CXL) initiative.

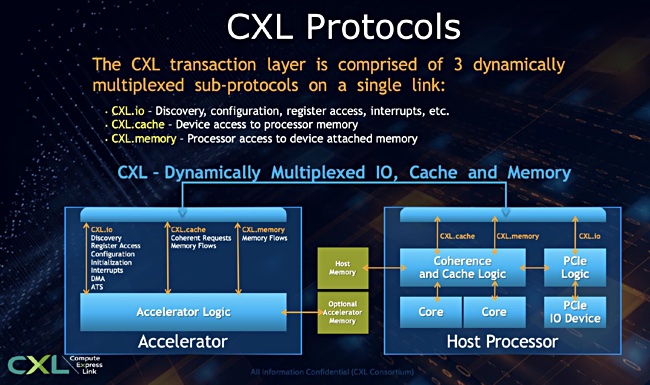

CXL is based on PCIe 5. We wrote in April last year: “CXL and Gen-Z technologies are read and write memory semantic protocols focused on low latency sharing of memory and storage resource pools for processing engines like CPUs, GPUs, AI accelerators or FPGAs.” At that time the two consortia announced a memorandum of understanding which opened the door to future collaboration on a combined CXL/Gen-Z specification.

It’s taken a long time — 19 months — for that effort to come into the open. But the two consortia have issued a joint statement saying they have signed “a Letter of Intent which, if passed and agreed upon by all parties, would transfer the Gen-Z Specifications and all Gen-Z assets to the CXL Consortium”.

Both organisations now want to focus on “the development of a memory coherent interface under the CXL Consortium with CXL as the sole industry standard moving forward”.

Jim Pappas, CXL Consortium board chairman and Hiren Patel, Gen-Z Consortium president, say in the statement: “We believe that this is the right step forward for our members and the industry ecosystem.”

Clearly this will avoid duplicating component interconnect development efforts and wasteful competitive work. It seems clear that CXL has more momentum that Gen-Z and a unified development will give up-stack developers of, for example, datacentre composability systems a single interconnect on which to base their efforts.