Kioxia research scientists have demonstrated hexa-level cell flash. That’s six bits per cell — 50 per cent more capacity than today’s QLC (four bits per cell)

A research paper describing the work was revealed at the fifth IEEE Electron Devices Technology and Manufacturing Conference (EDTM 2021) physical and virtual forum in April this year, which took place at Chengdu in China. The paper, “Cryogenic Operation of 3D Flash Memory for New Applications and Bit Cost Scaling with 6-Bit per Cell (HLC) and Beyond,” was judged to be the second-best paper at the event, and came to light in the Japanese PC Watch outlet in late July.

Today’s densest in-production flash cells are quad-level cells, having four bits per cell. This technology was achieved by starting from single-level cell (SLC) flash and increasing the number of possible threshold voltage levels in a cell:

- SLC = 0 or 1 — meaning two states and one threshold voltage;

- MLC = 00, 10, 01, or 11 — four states and so three threshold voltages;

- TLC = 000, 001, 010, 011, 100, 101, 110, 111 — eight states and thus seven threshold voltages;

- QLC = 0000, 0001, 0010, 0011, 0100, 0101, 0110, 0111, 1000, 1001, 1010, 1011, 1100, 1101, 1110, 1111 — 16 states and so 15 threshold voltages.

In general, each extra cell bit slows SSD speed and shortens its endurance. It also increases the complexity of the drive controller and the amount of error correction it has to do.

Nexsan, Pure Storage, StorONE and VAST Data all have QLC flash arrays in production.

Kioxia has previously demonstrated penta-level cell (PLC) technology:

- PLC = 00000, 00001, 00010, 00011, 00100, 00101, 00110, 00111, 01000, 01001, 01010, 01011, 01100, 01101, 01110, 01111, 10000, 10001, 10010, 10011, 10100, 10101, 10110, 10111, 11000, 11001, 11010, 11011, 11100, 11101, 11110, 11111 — 32 states and so 31 threshold voltages.

There has been no commercialisation of PLC NAND technology, presumably because the technology difficulties in producing PLC NAND with sufficient endurance and operational speed are currently insurmountable.

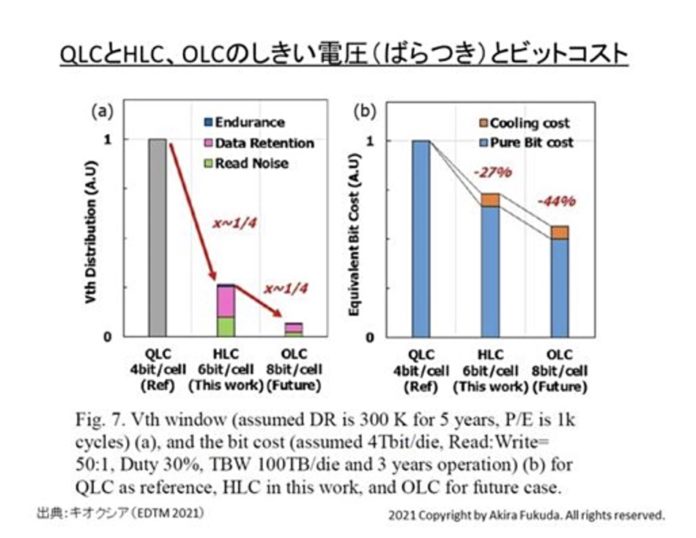

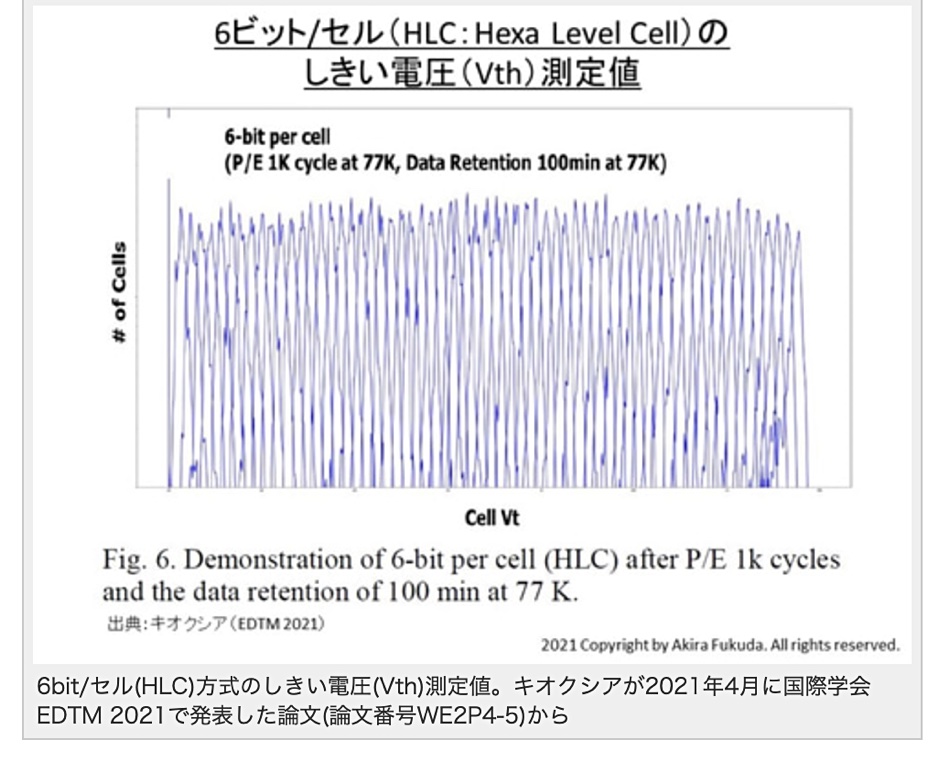

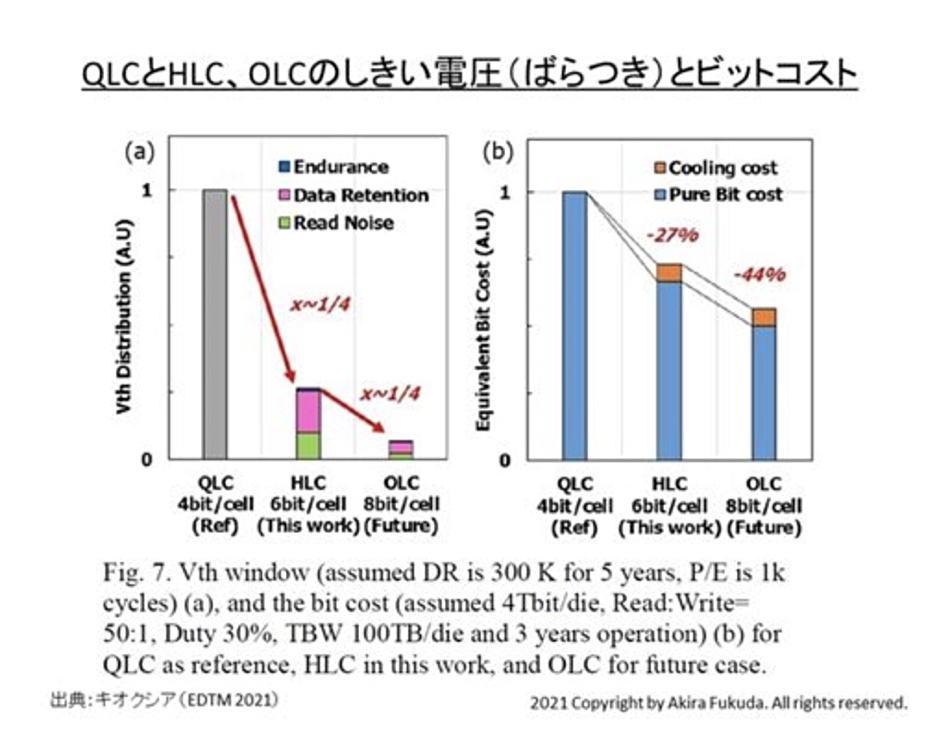

A hex-level cell will have 64 states and 63 threshold voltages — we won’t list all the binary values — and will have 20 per cent more capacity than a PLC cell. It will also have a lower endurance (PE cycles) with the raw value being 100 before the cell wears out.

The demonstration took existing Kioxia 3D NAND (the layer count was not revealed), and cooled it to the boiling point of liquid nitrogen — 77 K (-196° C) — by immersing it in that very cold fluid. But the actual controller operated at room temperature. This cooling reduced the variations in the threshold voltage, known as read noise. An insulating film in the cell maintains its structure better at the liquid nitrogen temperature level, with fewer tunnels being created.

Also, at room temperature, electrons in the charge capture element (film) are lost through thermionic emission and this lowers the threshold voltage. The liquid nitrogen cooling reduces the thermionic emission electron loss, so extending the cell’s endurance out to 1000 PE cycles.

The Kioxia scientists say that an eight-bit cell (Octa-Level Cell or OLC) is possible and that would have 256 voltage levels. They write that this would need a channel material changing from polycrystalline silicon to single crystal silicon or an equivalent material. They calculate that the bit cost with HLC and OLC NAND, even with the extra cooling involved, could make such drives cost-efficient. They suggest that seven-bits/cell (Septa-Level-Cell) might not be more cost-efficient than HLC, whereas OLC would be.

Is liquid nitrogen cooling a commercially feasible technology? It has been used by extreme PC Gamers to overclock CPUs but the technology has not been productised.

HLC is a super-interesting demo of what could be possible, but may have no real-world relevance. If we want to add 50 per cent more capacity to a QLC NAND drive it may be more feasible to up the layer count of its 3D NAND than the individual cell bit counts.

Bootnote

The paper’s presentation number was WE2P4-5 and the authors were Yuta Aiba, Hitomi Tanaka, Takashi Maeda, Keiichi Sawa, Fumie Kikushima, Masayuki Miura, Toshio Fujisawa, and Mie Matsuo of Kioxia Corporation, Japan.