Resistive RAM startup Weebit Nano has lifted the lid on its strategy to bring its ReRAM storage class memory to a fairly crowded market. B&F took a look.

Resistive RAM refers to random-access memory with two resistance states signalling a binary 1 or zero. ReRAM developers include Crossbar, SK hynix, and, back in 2016 at least, Western Digital. 4DS Memory and Dialog’s Adesto are also rivals in this space.

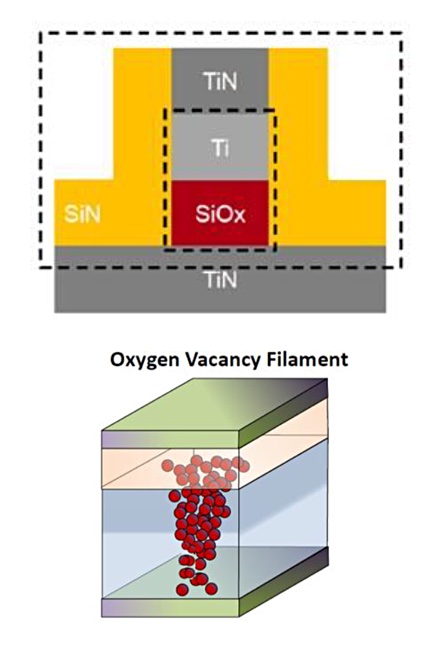

The actual technologies used to manipulate resistance vary, with SK hynix using phase-change memory, Weebit Nano using oxygen filament formation in a nano-porous SiOx (silicon oxide) material, and Crossbar also using filament formation in a silicon oxide material. All three suppliers say their technology is non-volatile and are using a crosspoint-style architecture in their chips, similar to Optane’s 3D XPoint design.

Weebit Nano was started up in Israel in 2014 by then-CEO Yossi Keret and is attempting to commercialise patented technology developed by Professor James Tour at Rice University (and licensed from there). Tour discovered that sending a current through silicon oxide could counteract its inherent insulator property and create a silicon crystal (oxygen vacancy) pathway or filament. Electrical pulses could then break and re-connect this filament, changing the resistance levels from low to high.

Financial engineering

Unusually Weebit IPO’d early, in 2016, on the Australian stock exchange using a piece of financial engineering; it performed a reverse-merger with Radar Iron, an Australian mining company. Since then it has raised a total of $21.3m in four equity rounds. Keret set up a collaboration with French technology research organisation CEA/Leti in 2016 to develop the technology as Weebit had no in-house capability,

Keret resigned as CEO in December 2017 but remained on the board. He’s now the CEO of Israeli startup Nanorobotics. Coby Hanoch took over in the Weebit CEO role in October 2017, and has a sales background in the ASIC and Electronic Design Automation space.

The picture we’re drawing here is that this is not a typical storage technology startup – based on their founders’ tech and going the VC funding route. Keret and Hanoch claim that Rice University’s ReRAM technology, apart from generally having DRAM-class speed (100ns write), and endurance (~1 million write cycles and 10-year retention) is relatively straightforward for adoption by semiconductor fabs. The idea seems to be that others – fabs – would build the products and license its tech.

Embedded and discrete memory

Weebit says the ReRAM materials involved are fab-friendly and can be easily and cost-effectively added to the final stages of a semi-conductor process – BEOL or back end of line – with a 2-mask adder and 5 – 8 per cent extra wafer cost. It is developing a product for the embedded memory market. Weebit needs a fab to build and sell chips using it, and said it expects to sign its first commercial agreement in the middle of this year.

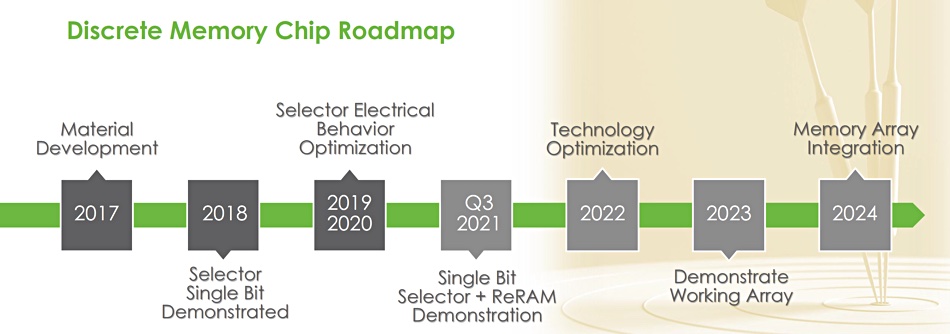

More interestingly from the enterprise storage point of view, it’s developing a discrete memory version of its technology. This requires the addition of a smaller selector (transistor) which enables isolating specific memory cells for a rewrite operation without altering the other cells. A quite large selector can be used in embedded memory but a smaller and low-power one is needed for discrete memory. This has been developed by Leti.

Weebit and partner Leti have filed a patent for this and another for a technology to enable multi-level cell operation – more than 1 bit/cell.

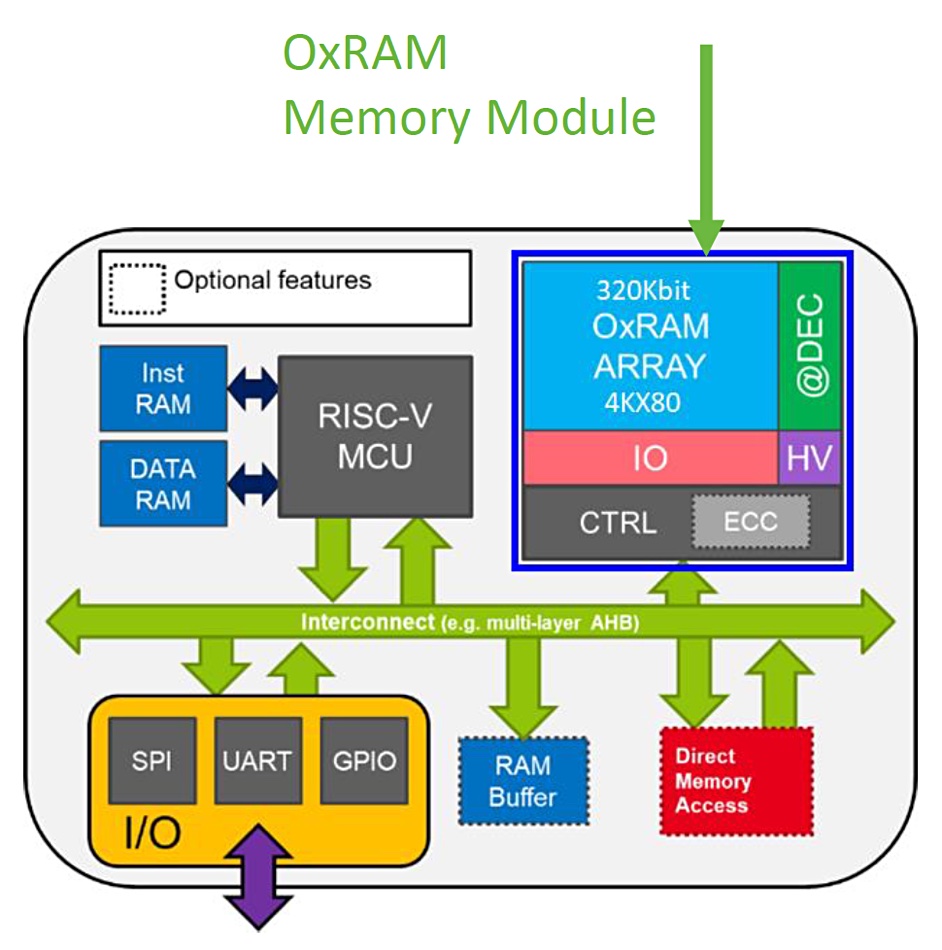

It’s developing a demonstration module incorporating its ReRAM (OxRAM) with a RISC-V microprocessor and peripherals, with silicon planned for the end of the year. Potential customers could then use the module as a platform on which to develop applications such as low-energy IoT devices, security products and sensors.

The first module silicon is planned for the end of the year. A demonstrable discrete ReRAM array could be delivered in 2023.

This is still early days in Weebit’s ReRAM technology development, and there is nothing concrete in the product sense yet. Park this storage-class memory candidate in the It-Might-Happen part of your mental landscape and don’t view it as any threat to Optane just yet.