Spin Memory has designed a ‘Universal Selector’ transistor that improves DRAM array density by 20 to 35 per cent, according to the company. It says the technology increases MRAM density by up to five times and accelerates MRAM operations.

Spin Memory derives its name from the field it works in. The company is a Spin Transfer Torque MRAM developer, which positions MRAM as a replacement memory technology for CPU caches using Static RAM. It claims its STT-MRAM could function as storage-class memory like Intel’s Optane.

Tom Sparkman, CEO of Spin Memory, provided an announcement quote: “Our latest breakthrough innovation allows for exciting new advancements and capabilities for [advanced memory] technologies – in addition to pushing MRAM into the mainstream market.”

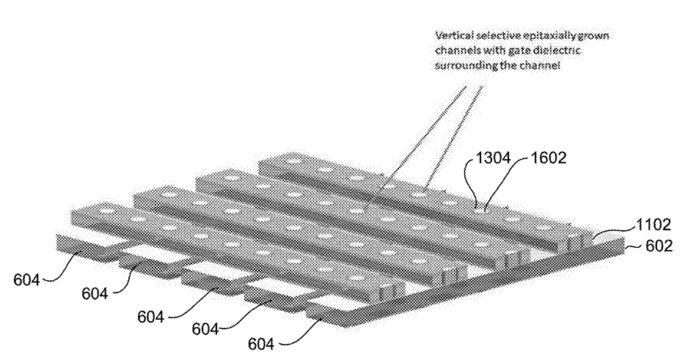

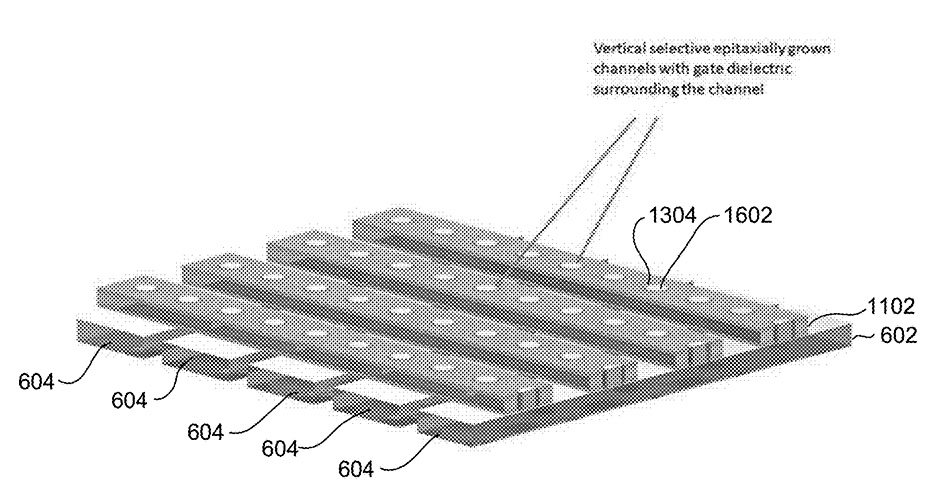

Spin Memory’s Universal Selector is, according to the announcement, a selective, vertical epitaxial cell transistor with a channel that is electrically isolated from the silicon substrate. Epitaxial refers to the growth of a crystal in a particular orientation on top of another crystal whose orientation determines the growth direction of the upper crystal. A vertical epitaxial cell is grown vertically above the underlying crystal. Epitaxy is used in semiconductor manufacturing to form layers and wells.

Spin Memory thinks this technology can be applied outside the MRAM field to DRAM, ReRAM and PCRAM, for example, hence the ‘universal’ attribute.

The electrical isolation prevents DRAM row hammer attacks, Spin Memory says.These are malware instances where repetitive (hammering) memory access patterns are made to to DDR3 and DDR4 cells, causing leakage and so altering cell contents in adjacent cell rows.

Charlie Slayman, IRPS 2020 technical program chair, was quoted in Spin Memory’s announcement: “Spin Memory’s Universal Selector offers a novel way to design vertical cell transistors and has been presented to the JEDEC task group evaluating solutions to the row hammering problem.”

Spin Memory claims Universal Selector gives any developer of non-Flash memories the means to “drastically improve density for almost every memory technology on the market without requiring an investment in specialised hardware or resources.”

Jim Handy of Object Analysis, an analyst firm, said: “This is a very clever use of the vertical transistors that are the basis of 3D NAND flash. If a vertical transistor can make NAND smaller, then why not harness it for other technologies?”

“Selectors have always been a vexing issue for emerging memories. A number of developers focus all of their effort on the bit element but none on the selector. Both are significant challenges and both need to be solved or you have nothing.”

Spin Memory has patented the Universal Selector – US 2020/0127052 AI. It will share additional technical details at the virtual 31st Magnetic Recording Conference on Thursday, August 20 at 10:40 a.m. PDT.