Two rival groups developing CPU-peripheral bus standards have agreed to work together.

The CXL and Gen-Z groups announced yesterday a memorandum of understanding, which opens the door for future collaboration. Blocks & Files expects a combined CXL-Gen-Z specification will be developed quickly and available before the end of the year.

Jim Pappas, CXL Consortium board chair, issued a quote: “CXL technology and Gen-Z are gearing up to make big strides across the device connectivity ecosystem. Each technology brings different yet complementary interconnect capabilities required for high-speed communications. We are looking forward to collaborating with the Gen-Z Consortium to enable great innovations for the Cloud and IT world.”

Gen-Z Consortium President Kurtis Bowman had this to say: “CXL and Gen-Z technologies work very well together, and this agreement facilitates collaboration between our organisations that will ultimately benefit the entire industry.”

The MOU

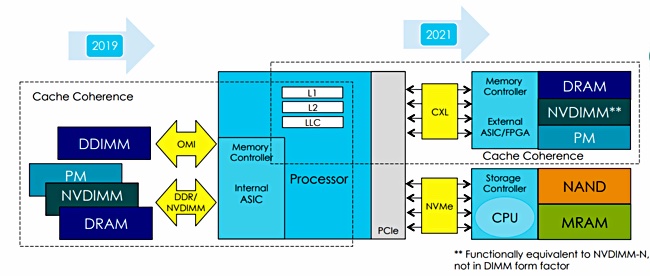

CXL and Gen-Z technologies are read and write memory semantic protocols focused on low latency sharing of memory and storage resource pools for processing engines like CPUs, GPUs, AI accelerators or FPGAs. CXL is looking at coherent node-level computing while Gen-Z is attending to fabric connectivity at the rack and row level.

The MOU between the two groups outlines the formation of common workgroups to provide cooperation and defines bridging between them.

Companies wishing to participate must simultaneously be a promoter or contributor member of the CXL Consortium and a general or associate member of the Gen-Z Consortium.

Why we need a new bus standard

Server CPUs, as they get more cores and link to GPUs with multiple engines, FPGAs, and ASICs, need a faster bus to link the data processing entities to memory and storage devices and other peripherals. Current bus technology is unable to transmit data fast enough to keep the processing engines busy.

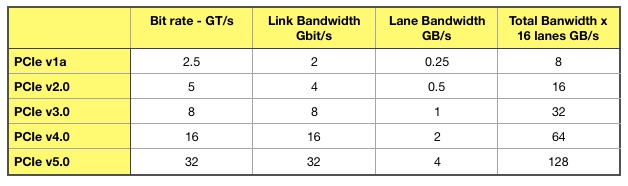

Today’s PCIe gen 3 bus is transitioning to PCI 4.0, which is twice as fast, and PCIe 5 is set to follow. But even PCIe 5.0 considered too slow for modern requirements. Accordingly, four consortiums have emerged to move bus technology standards forward: CXL, Gen-Z, CCIX and OpenCAPI.

We think CCIX and OpenCAPI are toast and will have to find niche technology areas to survive or merge somehow with CXL and Gen-Z.

Four buses in a row

The Compute Express Link (CXL) bus protocol specification means that CXL can run across a PCIe 5.0 link when it arrives. CXL is supported by the four main CPU vendors; AMD, ARM, IBM and Intel. Gen Z, OpenCAPI and CCIX have not attracted the same degree of CPU manufacturer support.

CXL is also supported by Alibaba, Cisco, Dell EMC, Facebook, Google, HPE, Huawei and Microsoft.

The Gen-Z consortium is supported by AMD, ARM, Broadcom, Cray, Dell EMC, Hewlett Packard Enterprise, Huawei, IDT, Micron, Samsung, SK hynix, Xilinx and others, but not Alibaba, Facebook and Intel. It has more than 40 members.

The CCIX (Cache Coherent Interconnect for Accelerators) was founded in January 2016 by AMD, ARM, Huawei, IBM, Mellanox, Qualcomm, and Xilinx – but not Nvidia or Intel.

The OpenCAPI (Open Coherent Accelerator Processor Interface) was established in 2016 by AMD, Google, IBM, Mellanox and Micron and other members are Dell EMC, HPE, Nvidia and Xilinx. OpenCAPI has been viewed as an anti-Intel group, driven by IBM.